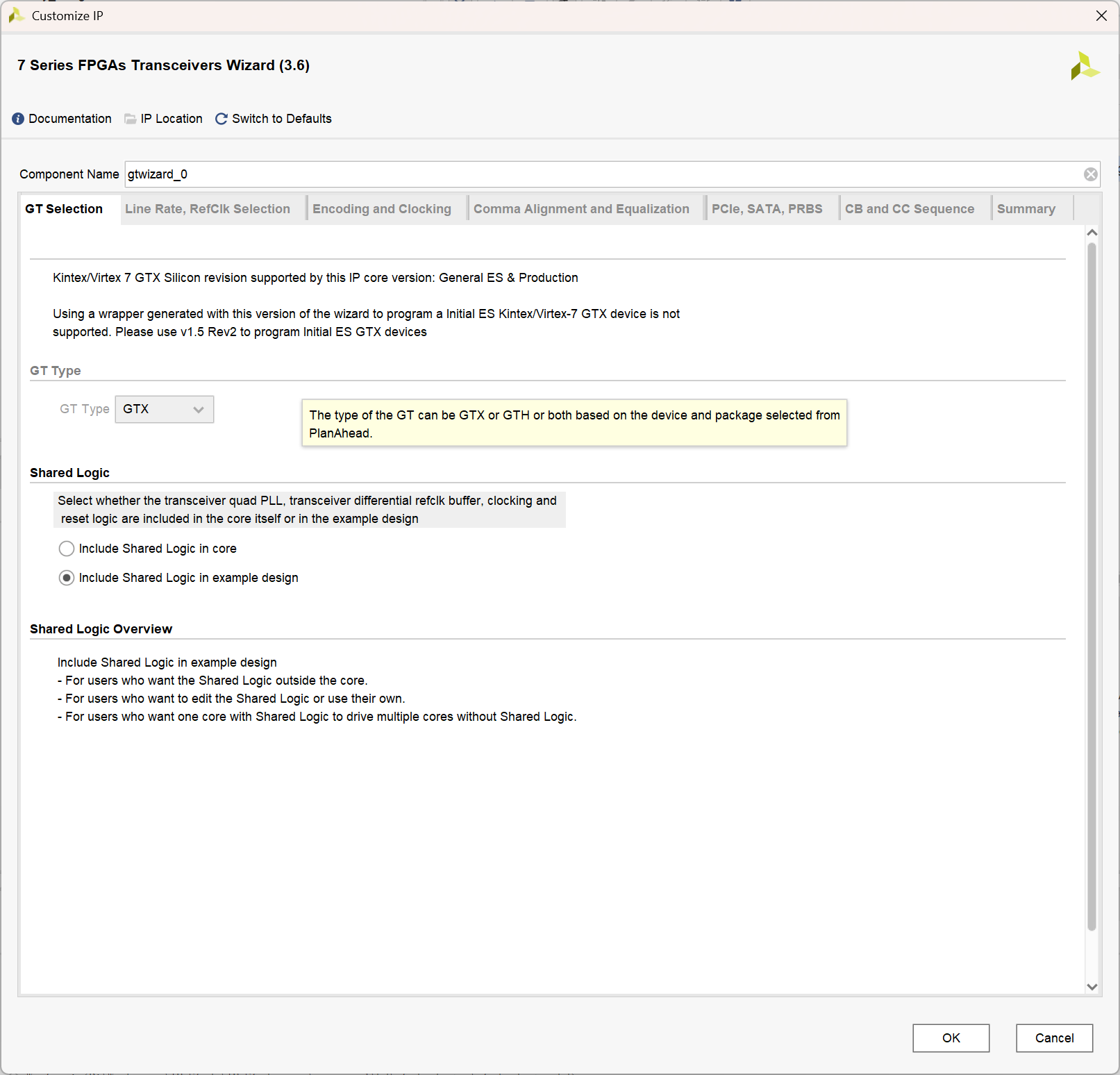

页面 1: GT Selection (GT 选择)

页面整体功能

这个界面是 Xilinx 7 系列 FPGA 高速收发器向导 (Transceivers Wizard) 的配置入口和第一个配置标签页 (GT Selection)。该向导用于帮助用户配置 FPGA 内部的高速串行收发器模块(如 GTX、GTH),以满足特定的通信协议(如 PCIe, SATA, Aurora, Ethernet 等)或自定义协议的需求。这个初始页面主要用于选择目标收发器类型 (GT Type) 和决定共享逻辑(如 QPLL、参考时钟缓冲器等)的放置方式。

界面内容详解

-

顶部信息栏

- Component Name (组件名称): gtwizard_0

解释: 这是将要生成的收发器 IP 核实例的名称。与 MIG 类似,这个名称将用于在 Vivado 工程中标识此 IP 核,并作为生成相关文件的基础名称。

建议: 可以使用默认名称,或修改为更具描述性的名称,如sata_gtx_core或aurora_channel_0_gt。 - 选项卡 (Tabs):

- GT Selection (GT 选择): 当前显示的标签页,用于选择 GT 类型和共享逻辑位置。

- Line Rate, RefClk Selection (线速率, 参考时钟选择): 后续页面,用于配置收发器的数据传输速率和参考时钟源频率及类型。

- Encoding and Clocking (编码与时钟): 配置数据编码方式(如 8b/10b, 64b/66b)和内部时钟结构。

- Comma Alignment and Equalization (同步字对齐与均衡): 配置用于数据流同步的特殊字符(Comma)以及接收端的均衡设置(DFE, LPM)以补偿信号损失。

- PCIe, SATA, PRBS: 可能包含针对特定协议(如 PCIe, SATA)的预设或用于测试的伪随机码序列 (PRBS) 生成/检查功能的配置。

- CB and CC Sequence (通道绑定与时钟校正): 配置多通道绑定和时钟偏差补偿相关的功能。

- Summary (摘要): 显示所有配置选项的汇总信息。

- Component Name (组件名称): gtwizard_0

-

GT Selection (GT 选择) 标签页内容

- 英文原文: "Kintex/Virtex 7 GTX Silicon revision supported by this IP core version: General ES & Production"

中文翻译: "此 IP 核版本支持的 Kintex/Virtex 7 GTX 芯片修订版本:通用工程样品 (General ES) 和量产 (Production) 版本"

解释: 表明当前这个版本的 Transceiver Wizard IP 支持(即已经过测试和验证)Kintex-7 和 Virtex-7 FPGA 中 GTX 收发器的通用工程样品和最终量产版本的芯片。 -

英文原文: "Using a wrapper generated with this version of the wizard to program a Initial ES Kintex/Virtex-7 GTX device is not supported. Please use v1.5 Rev2 to program Initial ES GTX devices"

中文翻译: "使用此版本向导生成的封装器 (wrapper) 来编程初始工程样品 (Initial ES) 的 Kintex/Virtex-7 GTX 器件是不支持的。请使用 v1.5 Rev2 版本来编程初始 ES GTX 器件。"

解释: 这是一个重要警告!对于最早期的工程样品芯片(被称为 Initial ES),不能使用当前这个版本的向导生成的代码/封装器,而必须使用一个更旧的特定版本(v1.5 Rev2)的向导。对于使用通用 ES 或量产芯片的用户,此条信息可以忽略。

- 英文原文: "Kintex/Virtex 7 GTX Silicon revision supported by this IP core version: General ES & Production"

-

GT Type (GT 类型) 部分:

- 下拉框

GT Type: GTX

解释: 选择你想要配置和使用的收发器硬核模块的类型。7 系列 FPGA 中主要包含 GTX 和 GTH 两种类型的收发器,它们在最高速率、功耗和功能上有所不同(GTH 通常更快)。

黄色提示框:

英文原文: "The type of the GT can be GTX or GTH or both based on the device and package selected from PlanAhead."

中文翻译: "GT 的类型可以是 GTX 或 GTH,或两者皆有,这取决于从 PlanAhead (Vivado) 中选择的器件和封装。"

解释: 这个下拉框中可供选择的 GT 类型(是只有 GTX,只有 GTH,还是两者都有)是由你在 Vivado 工程中设置的具体 FPGA 器件型号决定的。例如,某些 Artix-7 或 Kintex-7 器件可能只有 GTX,而高端的 Virtex-7 或 Zynq 器件可能同时拥有 GTX 和 GTH。向导会自动检测你的目标器件包含哪些类型的收发器。

建议: 必须根据你的目标 FPGA 器件所包含的、并且你打算在设计中使用的收发器类型来选择。 如果你的芯片只有 GTX,这里通常也只会显示 GTX。如果同时有 GTX 和 GTH,你需要根据你的应用(例如,协议要求的速率)来选择合适的类型。

- 下拉框

-

Shared Logic (共享逻辑) 部分:

- 英文原文: "Select whether the transceiver quad PLL, transceiver differential refclk buffer, clocking and reset logic are included in the core itself or in the example design"

中文翻译: "选择收发器 Quad PLL、收发器差分参考时钟缓冲器、时钟和复位逻辑是包含在核自身内部,还是包含在示例设计中"

解释: FPGA 中的高速收发器通常以 "Quad"(四个通道/Lane)为单位组织。同一个 Quad 内的多个收发器通道经常需要共享一些公共资源,最主要的就是 QPLL (Quad PLL,用于生成高速串行时钟) 和 差分参考时钟缓冲器 (IBUFDS_GTE*)。此外,还可能有一些相关的时钟生成逻辑和复位逻辑也是可以共享的。这个选项让你决定这些共享资源的逻辑是直接打包在你当前配置的这个gtwizard_0IP 核内部,还是放在 IP 核外部(由示例设计提供,或者后续由用户手动管理)。 - 选项 1:

Include Shared Logic in core(在核内包含共享逻辑)

解释: 选择此项,生成的gtwizard_0IP 核将包含它所需要的所有逻辑,包括那些共享资源(QPLL, RefClk Buffer 等)。这个 IP 实例会变得"自给自足"。 - 选项 2:

Include Shared Logic in example design(在示例设计中包含共享逻辑) (图片中选中此项)

解释: 选择此项,生成的gtwizard_0IP 核只包含其自身的通道逻辑 (Channel Logic),不包含共享的 QPLL、RefClk Buffer 等。这些共享逻辑需要在 IP 核外部单独实例化,并连接到gtwizard_0的相应端口上。向导通常会生成一个示例设计 (example_design) 来演示如何做这种连接。 - Shared Logic Overview (共享逻辑概述)

英文原文:

"Include Shared Logic in example design"

"- For users who want the Shared Logic outside the core."

"- For users who want to edit the Shared Logic or use their own."

"- For users who want one core with Shared Logic to drive multiple cores without Shared Logic."

中文翻译:

"在示例设计中包含共享逻辑"

"- 适用于希望共享逻辑位于核外部的用户。"

"- 适用于希望编辑共享逻辑或使用自己的共享逻辑的用户。"

"- 适用于希望用一个包含共享逻辑的核来驱动多个不包含共享逻辑的核的用户。"

解释: 这个列表详细说明了选择"在示例设计中包含共享逻辑"(即共享逻辑在核外部)的几种主要原因和应用场景:- 灵活性/层级化设计: 用户希望将共享资源作为一个独立的模块来管理,而不是混在某个通道的 IP 核里。

- 定制化: 用户可能想修改标准向导生成的共享逻辑,或者用自己设计的 PLL 或时钟缓冲方案来替代。

- 多通道/多核共享 (最常见原因): 当你需要使用同一个 Quad 内的多个收发器通道(Lanes)时,这些通道必须共享同一个 QPLL 和参考时钟缓冲器。如果每个通道的 GT Wizard IP 都选择"在核内包含共享逻辑",就会导致资源冲突和重复实例化。正确的做法是:

- 实例化一个 GT Wizard 核(或者一个专门的共享逻辑模块),选择包含共享逻辑。

- 为同一 Quad 内的其他通道实例化多个 GT Wizard 核,选择不包含共享逻辑(即选"在示例设计中包含...")。

- 然后将那些不含共享逻辑的核的 QPLL 和 RefClk 相关端口连接到那个包含共享逻辑的核或模块的对应输出上。

-

建议:

- 如果你只使用一个 Quad 内的一个或多个通道,并且打算让向导一次性配置好所有这些通道, 选择

Include Shared Logic in core可能更直接(但你需要确保在向导后续步骤正确配置多通道)。 - 如果你需要在一个 Quad 内实例化多个独立的 GT Wizard IP 核(例如,每个核配置一个通道),或者你需要对共享逻辑进行定制,或者追求更清晰的设计层次结构, 强烈推荐选择

Include Shared Logic in example design(共享逻辑在核外)。这是更灵活、更通用的做法,尤其适用于多通道设计。图片中默认选中此项也印证了其常用性。

- 如果你只使用一个 Quad 内的一个或多个通道,并且打算让向导一次性配置好所有这些通道, 选择

- 英文原文: "Select whether the transceiver quad PLL, transceiver differential refclk buffer, clocking and reset logic are included in the core itself or in the example design"

重要注意事项

资源冲突警告:如果你在同一个Quad内有多个通道,但每个通道的GT Wizard都选择了"在核内包含共享逻辑",会导致QPLL资源冲突!这可能会使设计无法正常工作或综合失败。在多通道设计中正确管理共享逻辑至关重要。

总结

这个 "GT Selection" 页面是配置高速收发器的第一步,核心是:

- 确认向导识别的 GT 类型 (GTX/GTH) 与你的 FPGA 和设计意图相符。

- 做出关于 共享逻辑 (QPLL, RefClk Buffer 等) 放置位置的关键决策。选择将共享逻辑放在核外部("in example design")通常能提供更大的灵活性,是多通道设计的标准做法。

最佳实践:对于大多数复杂设计,推荐将共享逻辑保留在示例设计中(即选择第二个选项)。这提供了更好的模块化设计,并允许多个收发器通道共享同一个QPLL,从而节省资源并确保正确的时钟分配。

理解共享逻辑的概念对于正确使用高速收发器至关重要。配置错误可能导致资源冲突或无法正常工作。